#### No. AN9752 September 1997

# **Application Note**

## Sync Stripper and Sync Inserter for Composite Video (HFA1115, HFA1135)

Authors: Mark Amarandos and Jeff Lies

#### Introduction

Sync signals are a necessary part of video systems, but it seems like they are often there when you don't want them, and conspicuously absent when you need one. Thus, two common functions required for processing analog video signals are sync strippers, to remove unwanted sync signals, and sync inserters to combine separate video and sync signals into one "composite" video signal. An ideal sync stripper or inserter should perform the desired function and drive at least one double terminated video load without degrading the video signal.

### Sync Stripper

In video systems it is frequently necessary to remove the sync pulse from a video signal, while passing the active video information. A familiar application for this is the scrambling of premium channels by cable operators so that they may only be viewed by authorized subscribers. The removal of the sync pulse makes it impossible for the television receiver to lock onto the video signal thus producing a highly distorted picture. Sync strippers are also useful for removing the sync pulse from video signals preceding A/D conversion. After removal of the sync pulse, the active video portion of the signal may be gained up to the full scale input range of the converter for better resolution.

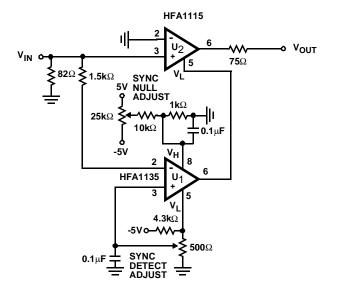

Figure 1 shows a composite video sync stripper composed of an Output Limiting Op Amp (U1) and a Programmable Gain, Output Limiting Buffer (U2). U2 is the video amplifier/driver, and is configured in a gain of 2 in order to provide an overall unity gain while driving a double terminated 75 $\Omega$  cable. Using the HFA1115 for U<sub>2</sub> (an HFA1113 may be used if higher bandwidth is needed for component video applications), rather than an op amp, saves board space because the gain setting resistors are inside the IC. U<sub>1</sub> is configured as a comparator and performs the sync detect function. The Sync Detect adjustment is nominally set for a comparator threshold of -0.2V, which sets it below the level of the active video information, but within the normal level for sync signals.

During a sync pulse, the output of the comparator  $(U_1)$ swings to the voltage set on its V<sub>H</sub> pin (approximately 0V in this case). The output of U1 drives the VL input of U2, so the video output (Vout) is prevented from swinging below GND, thereby removing the sync pulse. The Sync Null potentiome-

FIGURE 1. COMPOSITE VIDEO SYNC STRIPPER

ter sets the V<sub>H</sub> level of the comparator, and is adjusted for a 0V output from U<sub>2</sub> during the sync interval. This adjustment compensates for offset errors in the limiting circuitry of U1 and  $U_2$ .

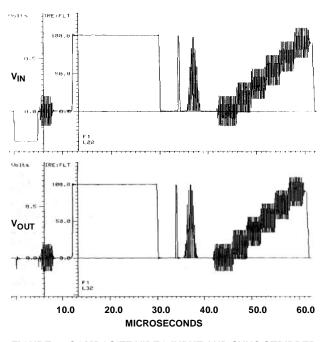

Figure 2 shows a comparison of the input (a composite NTSC test signal) and output waveforms of the sync stripper circuit. Note that the active portion of the composite video signal crosses below the blanking level (0V in this case). This is why a simple half wave rectifier, or a component video sync stripper (see HFA1103 data sheet and App Note AN9514) cannot be used as a composite video sync stripper. The circuit in Figure 1 removes the sync pulse while preserving the full range of the active video portion of the signal. During this active video, the comparator's output swings to the voltage defined by its VL input (approximately -2.5V), so no low limiting is applied to U<sub>2</sub>. Thus the video signal is passed by  $U_2$  with no limiting distortion.

This circuit does produce glitches at the sync edges that are a few nanoseconds wide, but most receivers will not recognize these glitches as sync pulses. In sensitive applications, these glitches can be reduced by a low pass filter.

#### CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2001. All Rights Reserved

FIGURE 2. COMPOSITE VIDEO INPUT AND SYNC STRIPPER OUTPUT

## Sync Inserter

In video distribution systems or video switchers, cost usually prevents assigning channels solely for sync signals. Therefore, sync signals are usually added to an active video channel, before running through the switcher or router, via a sync inserter circuit.

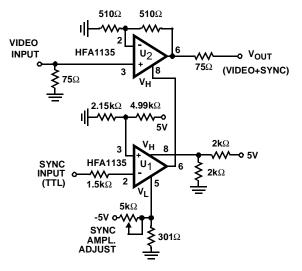

A simple variation of the circuit in Figure 1 may be used to insert sync pulses in video signals. If a properly timed TTL level pulse is applied to the Sync Input during the horizontal or vertical blanking interval, the circuit in Figure 3 inserts a negative sync pulse into the video signal applied at the Video Input.

FIGURE 3. SYNC INSERTION CIRCUIT

On the positive transition of the Sync Input signal, the comparator's (U<sub>1</sub>) output swings to the voltage defined at its V<sub>L</sub> input (approximately -0.8V). This drives the video amplifier's (U<sub>2</sub>) V<sub>H</sub> input to -0.8V (approximately), which forces it's output to approximately -0.6V, and yields a -300mV sync signal at the output of a double terminated cable (V<sub>OUT</sub>). The Sync Amplitude potentiometer can be adjusted to set the sync tip to the desired voltage.

Once the Sync Input returns to GND, the comparator output swings to 2.5V, as defined by its  $\rm V_{H}$  input, and the video amplifier is once again ready to pass the active video information.

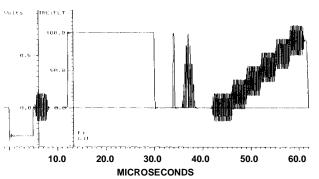

Figure 4 shows the output of the Sync Inserter which used the sync stripped output from Figure 2 as it's video input, and a positive TTL level pulse for its sync input.

FIGURE 4. OUTPUT FROM SYNC INSERTER CIRCUIT

If the Sync Input signal is an inverted TTL pulse, move the reference divider network from the noninverting to the inverting input, and connect the Sync Input (sans the  $1.5k\Omega$  resistor) to the noninverting input.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may resul from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com